Encodeurs et Décodeurs binaires / Binary Encoders and Decoders

Les circuits logiques / Logic circuit

8 to 3 Line encoder 16 to 4 Line encoder 32 to 5 Line encoder

3 to 8 Decoder / Demultiplexer 3 to 8 Decoder with timer

4 to 16 line Decoder / Demultiplexer 4 to 16 Decoder/Demultiplexer with Timer_LED

5 to 32 line Decoder 74HC138 5 to 32 line Decoder 74HC154

Sélecteur TTL (And Gate) Sélecteur TTL (Porte ET (AND), NON-OU (NOR), NON-ET (NAND))

|

Comme leur nom l'indique, les encodeurs transforment une

information plus longue en une valeur binaire plus courte. Il existe de nombreux types d'encodeurs, classés selon le nombre d'entrées et de sorties, ainsi que leur mode de fonctionnement. Cependant, tout encodeur obéit à une règle fondamentale : le nombre de lignes de sortie est toujours inférieur au nombre de lignes d'entrée. Cette section vous permettra d'en apprendre davantage sur les encodeurs : leur fonctionnement, leur utilité et leur rôle dans les circuits numériques. |

Encoders, as the name suggest,

encodes a larger bit of information into a smaller bit value.

There are many types of encoders based on the number of inputs and outputs and based on how it operates. But every Encoder has one underlying rule, the number of output lines on an Encoder will always be less than number of input lines. We will learn more about encoders, what is an encoder, how and why they are used in digital circuits in this section. |

|

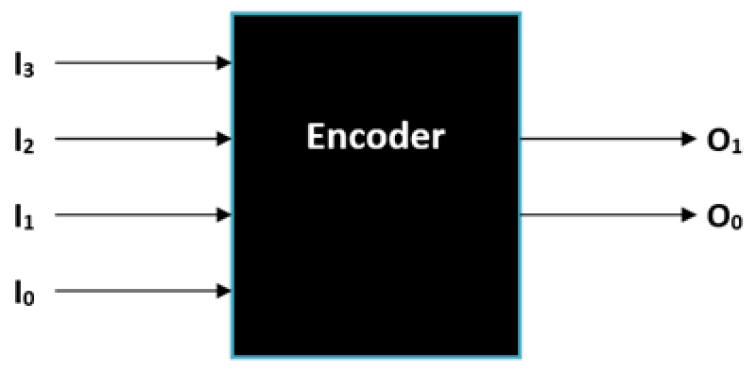

Principe de base d'un encodeur : Imaginons un encodeur comme une boîte noire, telle que représentée ci-dessous, qui réduit comme par magie le nombre de lignes d'entrée de 4 à seulement 2 lignes de sortie, tout en conservant la même information sans aucune perte de données. |

Basic Principle of Encoder:

Let us imagine an Encoder to be a black box as shown below which magically reduces the number of Input lines from 4 to just 2 output lines, but still provide the same information without any loss in data. |

|

|

|

Commençons par déterminer le nom de cet encodeur. Il possède quatre entrées et deux sorties ; son nom sera donc « encodeur 4:2 ». Si un encodeur possède « n » lignes de sortie, il possède alors (n=2) lignes d'entrée. Dans notre cas, il y a 2 lignes de sortie (n = 2), donc 4 lignes d'entrée (2 = 4), ce qui est bien le cas. Les quatre broches d'entrée sont numérotées de I0 à I3 et les deux broches de sortie de O0 à O1. Comment l'encodeur convertit-il quatre signaux en deux ? Le tableau de vérité ci-dessous l'explique. Il est également important de noter qu'un encodeur classique comme celui-ci fonctionne selon la règle suivante : à un instant donné, une seule broche d'entrée est à l'état haut. Dans la table de vérité suivant, une seule entrée sera donc à l'état haut. |

First let’s determine what the name of this Encoder would be. It has four inputs and two outputs so the name of this Encoder will be 4:2 Encoder. If an Encoder has “n” number of output lines then the number of input lines will be 2 in our case the number of output lines is two (n=2) hence the number of input lines should be be (2 = 4) four which is exactly the case. The four Input Pins are labelled from I0 to I3 and the two output pins are labelled from O0 to O1. So how do the Encoder convert four signals into two, it can be understood by taking a look at the truth table below. It is also important to know that an ordinary Encoder like the one shown here has a rule that at given time only one input pin should be high so in the following truth table only one input will be high. |

Table de vérité / Truth table

| In | Out | ||||

| I3 | I2 | I1 | I0 | O1 | O0 |

| 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

|

Le tableau de vérité ci-dessus présente toutes les configurations

possibles des entrées et des sorties. Par exemple, si seule la broche I0 est à l'état haut (1) et que toutes les autres entrées sont à l'état bas (0), les deux broches de sortie seront à l'état bas (0). De même, l'état des broches de sortie variera en fonction du contexte. Grâce à l'état de ces bits de sortie, l'utilisateur peut déterminer le signal d'entrée appliqué à l'encodeur. Mais à quoi sert la conversion de 4 lignes en 2 ? Nous avons présenté ici un encodeur 4:2 à titre d'exemple. Il existe d'autres encodeurs capables de traiter un plus grand nombre d'entrées et de les convertir en un nombre réduit de sorties, comme les encodeurs 8:3 et 16:4. Ces types d'encodeurs sont particulièrement utiles pour réduire le nombre de broches utilisées sur un microcontrôleur (MCU/MPU) ou le nombre de câbles de transmission dans un automate programmable (PLC) ou tout autre système comportant un réseau d'interrupteurs ou de LED. Il est également utilisé pour transmettre des données efficacement en utilisant moins de câbles. Dans certaines applications, il peut arriver que plusieurs entrées soient à l'état haut (1). Dans ce cas, on utilise un encodeur de priorité, que nous aborderons plus loin dans cet article. |

Every possible condition of the input the output is shown in the above

truth table. For instance when only I0 is high (1) and all the other inputs are low (0) then both the output pins will low (0). Similarly for each case the output pins will also change its status. By using this Output bits status the user will be able to trace back to what input signal would have been given to the Encoder. Okay, what is fancy about converting 4 lines to 2 lines why do we even need it? For the purpose of understanding we have explained a 4:2 Encoder. But there are other encoder which can taken a higher number of inputs and convert them to lower number of outputs like the 8:3 Encoder, 16:4 Encoder etc. These types of Encoder are very useful when we have to reduce the number of pins used on a MCU/MPU or reduce the number of signal carrying wires in PLC and other systems where an array of switch or LED. It is also used in transmitting data ef ciently by using lesser wires. In some applications we might have a situation where more than one input could be high (1). In those case we will something called Priority Encoder which we will discuss further in this article. |

|

Conception d'encodeurs à l'aide de circuits logiques combinatoires Maintenant que nous savons comment fonctionne un encodeur et où il est utilisé, Apprenons à en construire un à l'aide de portes logiques simples. Bien que des encodeurs comme le 8:3 soient disponibles sous forme de circuits intégrés compacts à boîtier unique, tels que le SN74LS148, il est important de comprendre leur fonctionnement afin de pouvoir créer des encodeurs personnalisés pour nos projets, en fonction de la table de vérité requise. Expression booléenne : La première étape de la conception d'un circuit logique combinatoire consiste à déterminer l'expression booléenne de sa table de vérité. C'est très simple et cela se trouve facilement en consultant la table de vérité. La table de vérité que nous avons vue précédemment est reproduite ci-dessous, accompagnée d'illustrations pour une meilleure compréhension. |

Building Encoders using Combinational Logic Designs Now that we know how an Encoder works and where it is used. Let us learn how to build one using simple logic gates. Although Encoders like 8:3 is available as neat single package IC like SN74LS148, it is important to know how they are built so that we can make custom encoders for our projects based on the required truth table. Boolean Expression: The rst in designing the Combinational Logic device is to nd the Boolean Expression for the truth table. It is very easy and can be easily determined just by looking at the truth table. The same truth table that we saw earlier is given below with some illustrations to make you understand better. |

In

Out

I3

I2

I1

I0

O1

O0

0

0

0

1

0

0

0

0

1

0

0

1

0

1

0

0

1

0

1

0

0

0

1

1

|

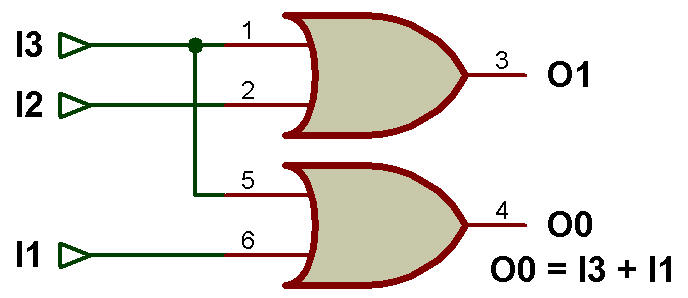

Le nombre d'expressions est égal au

nombre de lignes de sortie. Ici, nous avons deux sorties, donc deux expressions. Pour la première sortie O0, il suffit de vérifier dans quelle condition elle est à l'état haut (1) et de repérer la broche d'entrée correspondante qui reste également à l'état haut (1). De même, pour chaque valeur haute de O0, notez la broche d'entrée correspondante et additionnez les valeurs de ces broches. Les broches d'entrée correspondant à la sortie O0 sont surlignées en rouge ci-dessus, et celles correspondant à O1 en bleu. Ainsi, les expressions pour O0 et O1 sont : O1 = I3 + I2 O0 = I3 + I1 |

The number of expressions will be

equal to the number of output lines, here we have two outputs and hence

we have two Expressions. For the rst output O0, just check at which condition it is high (1) and trace the corresponding input pin number which also remains high (1). Similarly for all high values of O0 note which input pin number is high and add the pins. The input pins corresponding to Output pin O0 is highlighted in red above and for O1 is highlighted in Blue. So the Expression for O0 and O1 willbe O1 = I3 + I2 O0 = I3 + I1 |

|

Schéma du circuit encodeur 4:2

: Une fois l’expression booléenne obtenue, il suffit de la représenter sous forme de portes logiques. Ici, puisqu’il s’agit d’une addition (+), nous utiliserons des portes OU pour construire notre circuit. Vous pouvez également simplifier ou modifier l’expression booléenne selon vos besoins. Le schéma du circuit correspondant à l’expression ci-dessus est présenté ci-dessous. |

4:2 Encoder Circuit Diagram: Once we obtain the Boolean Expression we just have to draw it in form of Gates. Here since we have addition (+) operation we will use the OR gates for constructing our circuits. You can also simplify or modify the Boolean expression according to your needs. The circuit diagram for the above expression is shown below |

|

|

|

Ce circuit peut être facilement

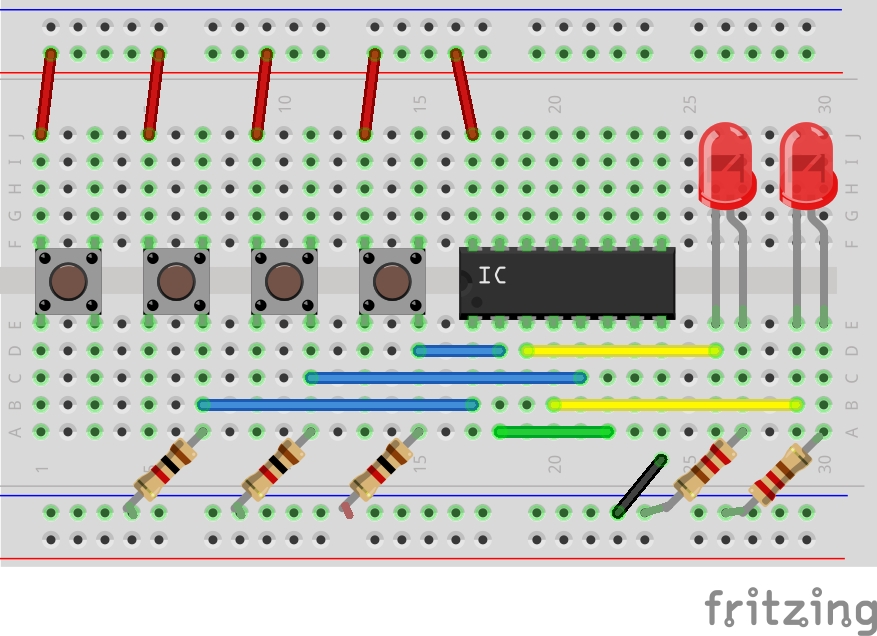

réalisé à l'aide d'un circuit intégré OR 4071 ou 7432. J'ai monté mon circuit d'encodeur sur une plaque d'essai, comme illustré ci-dessous. |

The circuit can easily built using a

4071 or 7432 OR gate IC. I have built my encoder circuit over a breadboard as shown below. |

|

0 = 00 1 = 01 2= 10 3 = 11 |

|

|

|

|

|

|

Les quatre entrées (I0, I1, I2 et I3)

sont gérées par les quatre boutons-poussoirs.

Lorsqu'un bouton est enfoncé, il applique une tension de +5 V à la broche, ce qui la met à l'état logique 1. Lorsqu'il n'est pas enfoncé, la broche est reliée à la masse par une résistance de rappel à la masse de 1 kΩ, ce qui la met à l'état logique 0. Les sorties (O0 et O1) sont représentées par deux LED rouges. Si la LED est allumée, la sortie est à l'état logique 1 ; si elle est éteinte, la sortie est à l'état logique 0. Comme vous pouvez le constater, lorsque le premier bouton est enfoncé, l'entrée I0 passe à l'état haut et les deux sorties restent donc à l'état bas (I0 n'est pas connecté). Lorsque le deuxième bouton est enfoncé, l'entrée I1 est activée et une LED s'allume pour indiquer que O0 est à l'état haut. Enfin, lorsque le quatrième bouton est enfoncé, l'entrée I3 passe à l'état haut et les deux LED s'allument. Il s'agit d'un circuit très simple, ce qui nous a permis de le réaliser facilement sur une plaque d'essai. Cependant, pour des encodeurs pratiques, le circuit sera un peu plus complexe. Des encodeurs sont également disponibles sous forme de circuits intégrés, que vous pouvez acheter si cela convient à votre projet. |

The four input lines (I0, I1, I2 and

I3) are provided by the four push buttons.

When the button is pressed it links +5V to the pin making it logic 1 and when the button is not pressed the pin is held to ground through a 1k pull down resistor to make it logic zero. The outputs (O0 and O1) are represented using a pair of red LED. If the LED glows then it means that the output logic is 1 and if they are turned off then it means that the output logic 0. As you can see when the rst button is pressed the input I0 is made high and hence both the outputs remain low (I0 not connected). When the second button is pressed the input I1 is turned on and thus one LED goes high to indicate O0 is high. Finally when the fourth button is pressed the input I3 is made high and thus both the LED goes high. This is a very simple circuit hence we have built it easily on a breadboard. But, for practical encoders the circuit will get a bit more complex. However Encoders are also available as IC packages which can be purchased if it suits your project. |

|

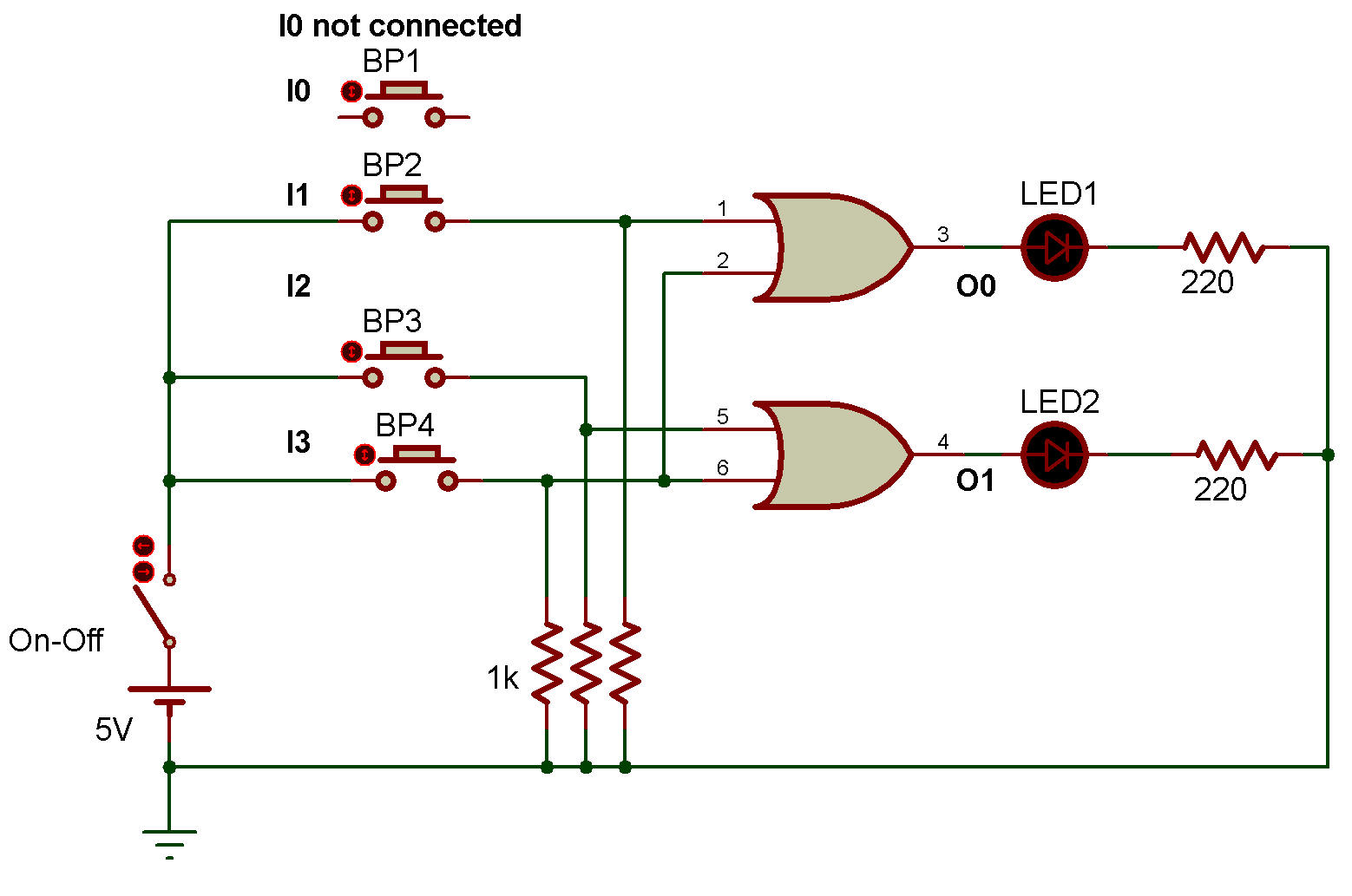

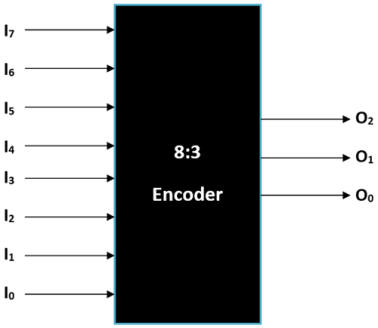

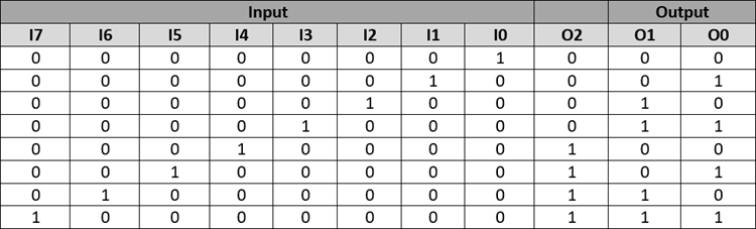

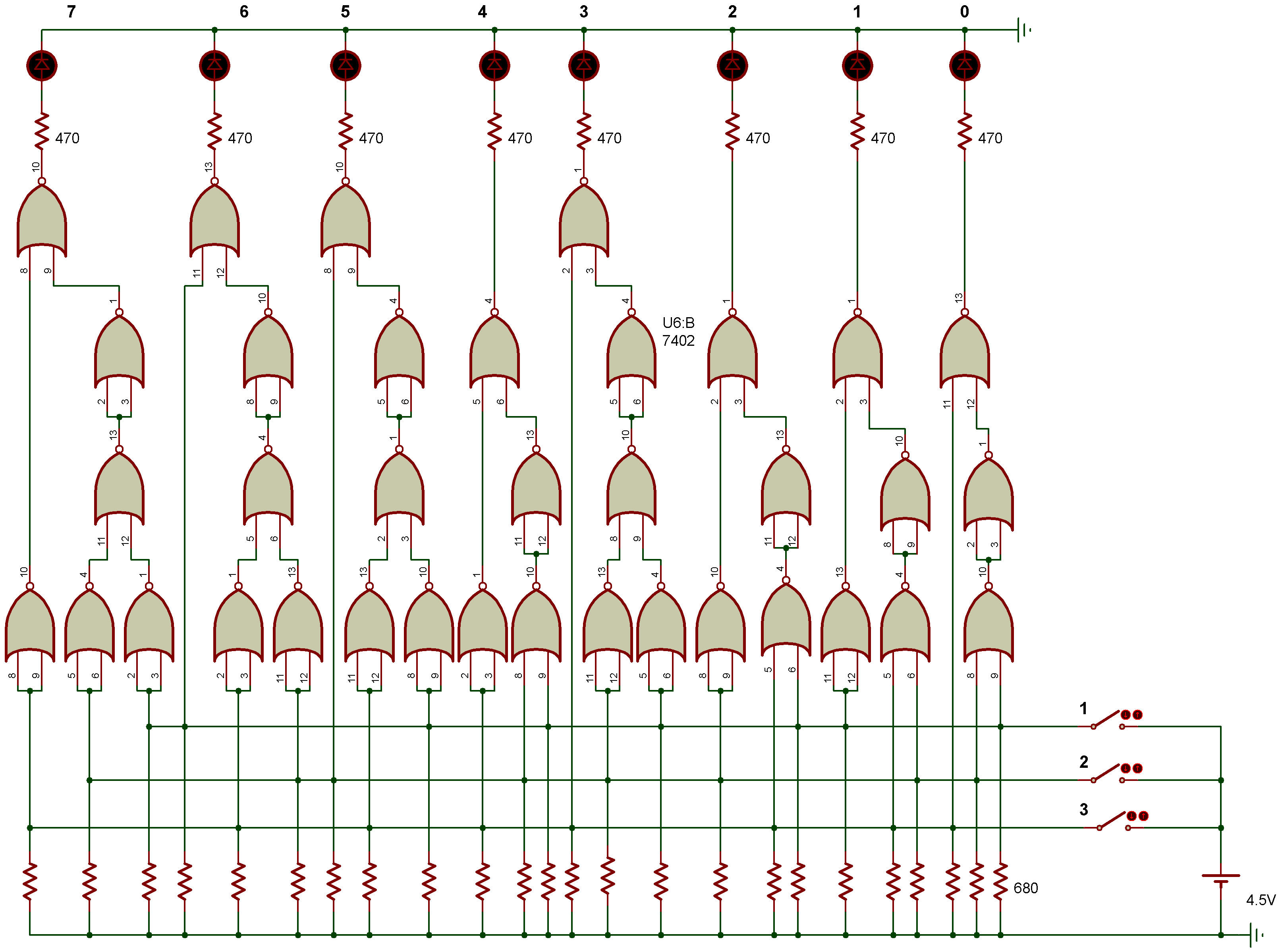

Encodeur 8:3 : Le fonctionnement et l'utilisation d'un encodeur 8:3 sont similaires à ceux d'un encodeur 4:2, à l'exception du nombre de broches d'entrée et de sortie. L'encodeur 8:3 est également appelé encodeur octal-binaire. Son schéma fonctionnel est présenté ci-dessous : |

8:3 Encoders: The working and usage of 8:3 Encoder is also similar to the 4:2 Encoder except for the number of input and output pins. The 8:3 Encoder is also called as Octal to Binary. Encoder the block diagram of an 8:3 Encoder is shown below: |

|

|

|

Ici, l'encodeur possède 8 entrées et 3 sorties. Une seule entrée doit

être à l'état haut (1) à un instant donné. Comme il y a 8 entrées, on parle d'entrée octale, et comme il y a trois sorties, on parle également de sortie binaire. La table de vérité de l'encodeur est présentée ci-dessous. |

Here the Encoder has 8 inputs and 3 outputs, again only one input should

be high (1) at any given time. Since there are 8 inputs it is called as octal input and since there are three outputs it’s also called binary output. The truth table of the Encoder is shown below. |

|

|

|

Expression booléenne : Puisque nous avons trois sorties, nous aurons trois expressions, comme indiqué ci-dessous : |

Boolean Expression: Since we have thee outputs we will have three expressions as shown below: |

|

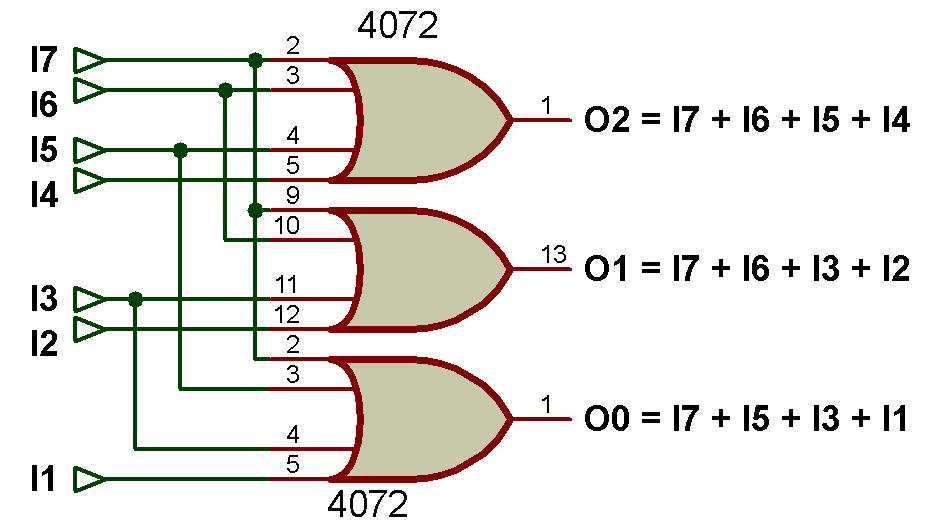

O0 = I7 + I5 + I3 + I1 O1 = I7 + I6 + I3 + I2 O2 = I7 + I6 + I5 + I4 |

0 = 000 1 = 001 2 = 010 3 = 011 4 = 100 5 = 101 6= 110 7 = 111 |

|

8.3 Schéma du circuit encodeur : Une fois l’expression booléenne obtenue, comme d’habitude, nous pouvons construire le schéma du circuit à l’aide des portes OU, comme illustré ci-dessous. Le circuit utilise un circuit intégré de porte OR à 4 entrées ; vous pouvez également simplifier l'expression booléenne pour utiliser d'autres circuits intégrés de porte à 2 entrées classiques. |

8:3 Encoder Circuit Diagram: Once the Boolean expression is obtained as always we can build the circuit Diagram using the OR gates as shown below. The circuit uses a 4-input OR gate IC, you can also simplify the Boolean Expression to use other normal 2 input Gate IC’s. |

|

|

|

Inconvénients des encodeurs classiques : Ces encodeurs présentent les inconvénients majeurs suivants : Lorsqu'aucune entrée n'est à l'état haut, la sortie est nulle. Or, cette condition est incompatible avec le fait que le bit de poids fort (MSB) soit à l'état haut. Il est donc impératif de s'assurer qu'au moins un bit reste toujours à l'état haut. Lorsque plusieurs entrées sont à l'état haut, la sortie est confondue et peut renvoyer le résultat de n'importe quelle entrée, ce qui peut prêter à confusion. Pour pallier ces difficultés, on utilise un autre type d'encodeur, appelé encodeur prioritaire. Ce dernier utilise une sortie supplémentaire pour déterminer la validité de la sortie. Lorsqu'il y a plusieurs entrées à l'état haut, seule celle qui passe à l'état haut en commençant par le bit de poids faible (LSD) est prise en compte, les autres étant ignorées. |

Drawback of Normal Encoders: These types of Encoders suffer from the following major drawbacks When none of the input is high the Output will be equal all zero. But this conditions also con icts with the rst bit being high (MSB). Hence care should always be taken that at least any one bit stays ON always. When more than one input is high, the output will be collapsed and can give the result for either one of the input which leads to confusion. To overcome these dif culties we employ a different type of encoder called a Priority Encoder. Which uses an additional output to determine if the output is valid, and when more than one input is help high the one that goes high starting from the LSD is alone considered while ignoring the other inputs. |

|

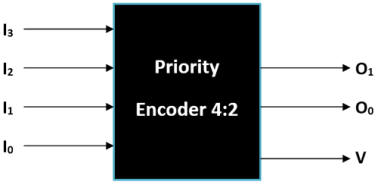

Encodeur prioritaire : Analysons un encodeur à priorité 4:2 à titre d'exemple, afin de comprendre en quoi il diffère d'un encodeur classique et comment il permet de surmonter les deux inconvénients mentionnés précédemment. Le schéma fonctionnel d'un encodeur à priorité 4:2 est présenté ci-dessous : |

Priority Encoder: Let us analyse a 4:2 Priority Encoder as an example to understand how it differs from a normal Encoder and it can overcome the above mentioned two drawbacks. The block diagram of a 4:2 Priority Encoder is shown below: |

|

|

|

Un encodeur prioritaire 4:2 possède également 4 entrées et 2 sorties,

mais nous ajouterons une sortie supplémentaire, appelée V, pour « bit de

validité ». Ce bit de validité vérifie si les quatre broches d'entrée sont à l'état bas (0). Si c'est le cas, le bit se met également à l'état bas, indiquant ainsi que la sortie n'est pas valide. Nous pouvons ainsi pallier le premier inconvénient mentionné précédemment. |

A priority 4:2 Encoder also has 4 inputs and 2 outputs, but we will add

another output called V which stands for valid bit. This valid bit will check if all the four input pins are low (0). If low the bit will also make itself low stating that the output is not valid thus we can overcome the rst drawback mentioned above. |

|

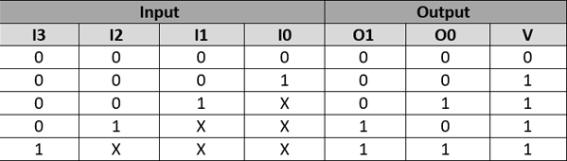

4.2 Table de vérité de l'encodeur prioritaire : L'inconvénient suivant peut être évité en donnant la priorité aux bits de poids fort (MSB). L'encodeur vérifie à partir du MSB et, dès qu'il trouve le premier bit à l'état haut (1), il génère la sortie correspondante. Ainsi, l'état haut ou bas des autres broches est indifférent. Par conséquent, dans le tableau de vérité ci-dessous, lorsqu'un 1 est atteint, les valeurs indifférentes sont représentées par « X ». |

4:2 Priority Encoder Truth Table: The next drawback can be avoided by giving priority to MSB bits. The Encoder will check from the MSB and once it nds the rst bit that high (1) it will generate the output accordingly. So it does not matter if the other pins are high or low. Hence in the truth table below once a 1 is reached the don’t care values are presented by “X”. |

|

|

|

Expression booléenne / Boolean Expression: O1 = I3 + I2 O0 = I2 I1' + I3 V = I3 + I2 + I1 + I0 |

|

|

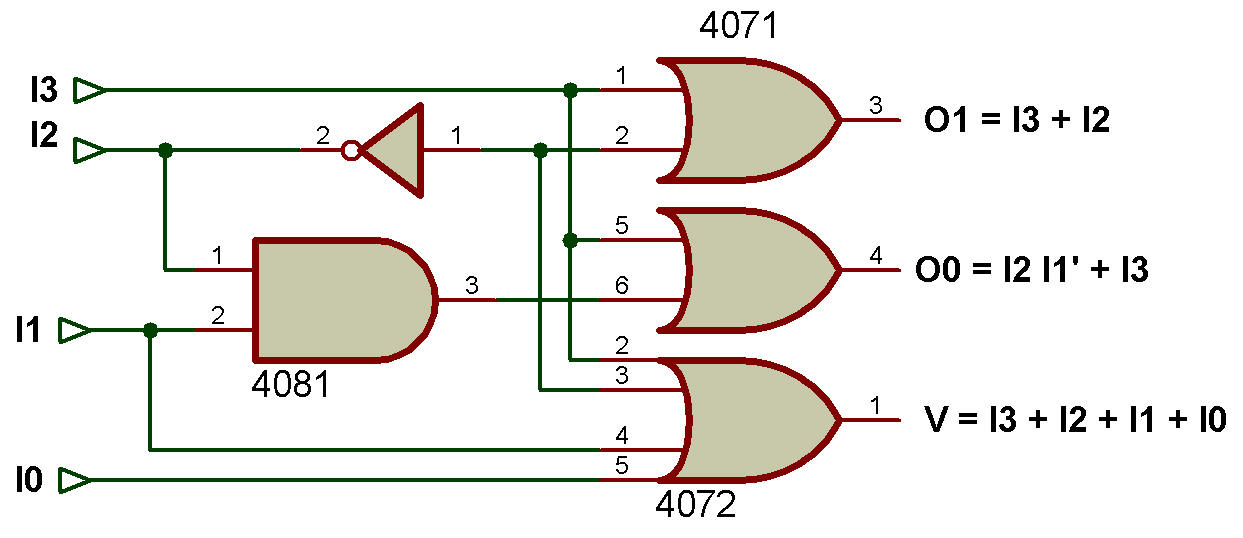

Schéma du circuit : Le schéma du circuit de ce projet peut être construit à l’aide d’expressions booléennes. |

Circuit Diagram: The circuit diagram for this project can be build using the Boolean expressions. |

|

|

|

Le circuit peut être construit à l'aide des portes logiques NON, ET et

OU. Les bits O0 et O1 sont considérés comme des sorties, tandis que le bit V sert à valider la sortie. La sortie est prise en compte uniquement si le bit V est à l'état haut. Si sa valeur est à l'état bas (0), la sortie est ignorée, car cela implique que toutes les entrées sont à zéro. Pour un encodeur prioritaire 8:3, utilisez un 74148, 74LS148 ou 74HC148. |

The circuit can be build using the basic NOT, AND, and OR gates. Here the bits O0 and O1 are considered as outputs while the bit V is use to validate the output. Only if the bit V is high, the output will be considered. If the value of V is low (0) the output should be ignored, since it implies that all the input pins are zero. For 8:3 priority encoder use a 74148, 74LS148 or 74HC148 |

|

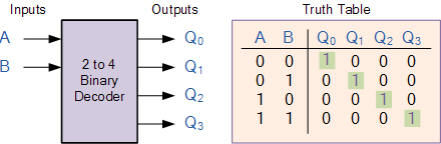

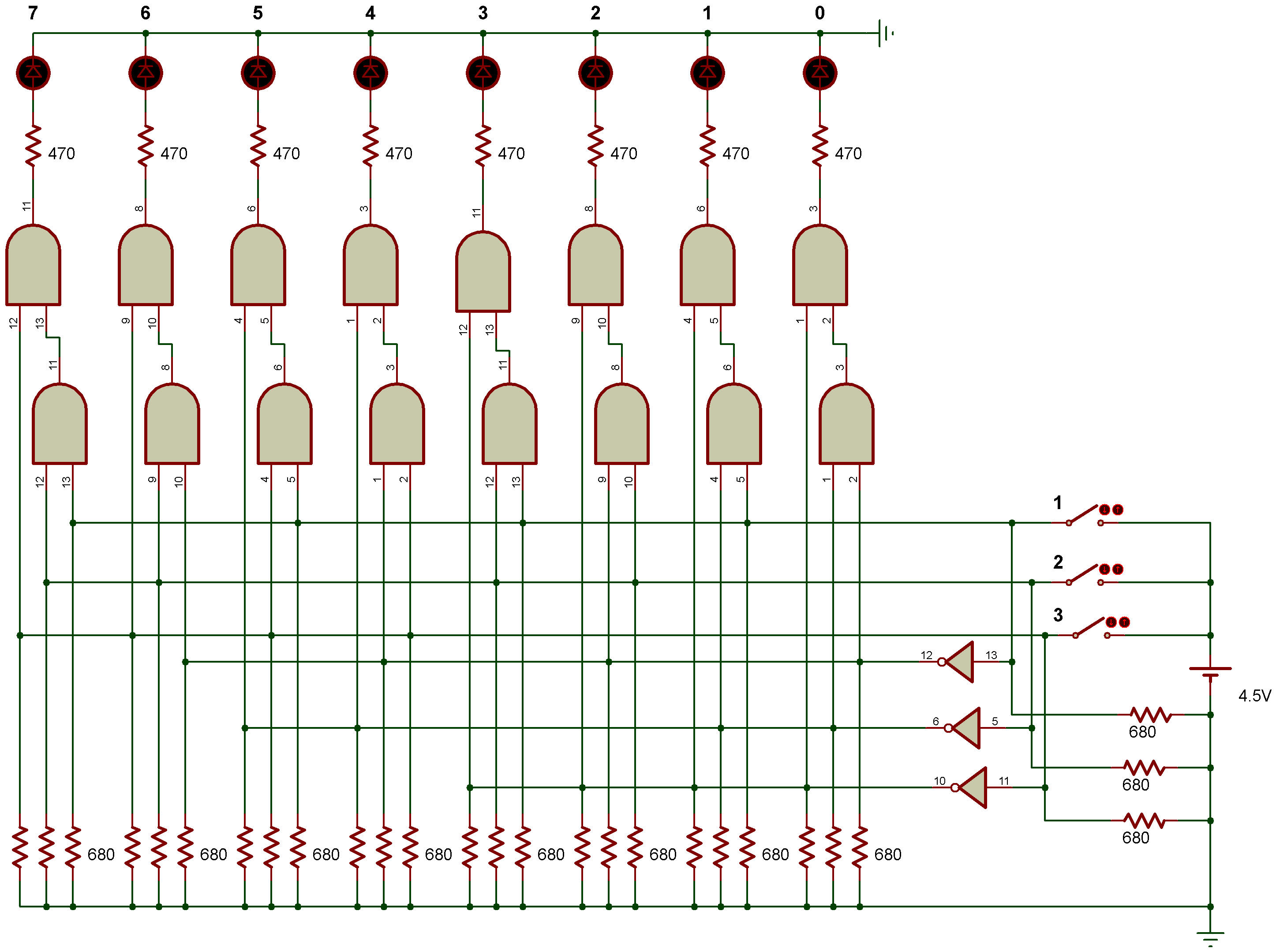

Décodeur binaire Un décodeur binaire est un circuit logique combinatoire constitué de portes logiques individuelles. Son fonctionnement est exactement l'inverse de celui d'un encodeur. Le terme « décodeur » désigne la conversion ou le décodage d'informations codées d'un format à un autre. Un décodeur binaire transforme donc n signaux d'entrée binaires en un code équivalent utilisant 2n sorties. |

Binary Decoder Binary Decoder is another combinational logic circuit constructed from individual logic gates and is the exact opposite to that of an Encoder The term “Decoder” means to translate or decode coded information from one format into another. So a binary decoder transforms “n” binary input signals into an equivalent code using 2n outputs. |

|

Les décodeurs binaires sont un autre type de circuit logique numérique.

Ils acceptent des codes de 2, 3 ou 4 bits en fonction du nombre de lignes d'entrée de données. Un décodeur possédant un ensemble de deux bits ou plus est donc défini comme ayant un code de n bits, et peut ainsi représenter 2ⁿ valeurs possibles. Un décodeur convertit généralement une valeur binaire en une valeur non binaire en activant une seule de ses n sorties à l'état logique « 1 ». Si un décodeur binaire reçoit n entrées (généralement regroupées en un seul nombre binaire ou booléen), il active une seule de ses 2ⁿ sorties en fonction de cette entrée, toutes les autres restant désactivées. |

Binary Decoders are another type of digital logic device. That has inputs of 2-bit, 3-bit or 4-bit codes depending upon the number of data input lines. So a decoder that has a set of two or more bits will be defined as having an n-bit code, and therefore it will be possible to represent 2n possible values. Thus, a decoder generally decodes a binary value into a non-binary one by setting exactly one of its n outputs to logic “1”. If a binary decoder receives n inputs (usually grouped as a single Binary or Boolean number) it activates one and only one of its 2n outputs based on that input with all other outputs deactivated. |

|

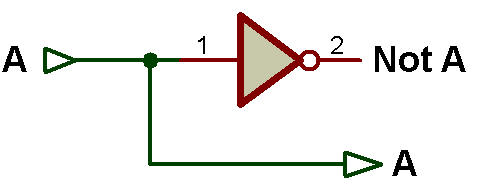

Ainsi, par exemple, un inverseur (porte NON) peut être classé comme un

décodeur binaire 1 à 2 car 1 entrée et 2 sorties (21) est possible car

avec une entrée A, il peut produire deux sorties A et non-A comme

indiqué. |

So for example, an inverter ( NOT-gate ) can be classed as a 1-to-2

binary decoder as 1-input and 2-outputs (21) is possible because with an

input A it can produce two outputs A and not-A as shown. |

|

|

|

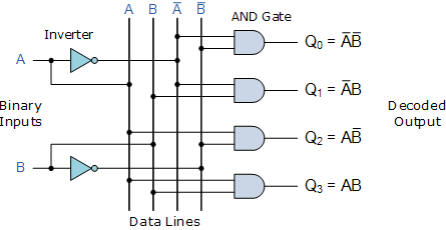

On peut donc dire qu'un décodeur logique combinatoire standard est un

décodeur n vers m, où m ≤ 2n, et dont la sortie Q dépend uniquement de

ses entrées actuelles. Autrement dit, un décodeur binaire examine ses entrées, détermine le code binaire (ou nombre binaire) présent et sélectionne la sortie correspondante. Un décodeur binaire convertit des entrées codées en sorties codées, les codes d'entrée et de sortie étant différents. Il existe des décodeurs capables de décoder un signal d'entrée binaire ou BCD (code 8421) en un code de sortie décimal. Les décodeurs BCD-décimal couramment disponibles incluent le TTL 7442 ou le CMOS 4028. En général, le code de sortie d'un décodeur comporte plus de bits que son code d'entrée. Les circuits de décodage binaire pratiques comprennent les configurations 2 vers 4, 3 vers 8 et 4 vers 16 lignes. Voici un exemple de décodeur 2 vers 4 lignes, accompagné de sa table de vérité : |

Then we can say that a standard combinational logic decoder is an n-to-m

decoder, where m ≤ 2n, and whose output, Q is dependent only on its

present input states. In other words, a binary decoder looks at its current inputs, determines which binary code or binary number is present at its inputs and selects the appropriate output that corresponds to that binary input. A Binary Decoder converts coded inputs into coded outputs, where the input and output codes are different. Decoders are available to “decode” either a Binary or BCD (8421 code) input pattern to typically a Decimal output code. Commonly available BCD-to-Decimal decoders include the TTL 7442 or the CMOS 4028. Generally a decoders output code normally has more bits than its input code. And practical “binary decoder” circuits include, 2-to-4, 3-to-8 and 4-to-16 line configurations. An example of a 2-to-4 line decoder along with its truth table is given as: |

|

0 = 00 1 = 01 2 = 10 3= 11 |

|

L'exemple simple ci-dessus d'un décodeur binaire 2 vers 4 lignes est

constitué d'un réseau de quatre portes ET. Les deux entrées binaires A et B sont décodées en l'une des quatre sorties, d'où l'appellation de décodeur binaire 2 vers 4. Chaque sortie représente un des minitermes des deux variables d'entrée (chaque sortie = un miniterme). Les entrées binaires A et B déterminent quelle ligne de sortie, parmi Q0 à Q3, est à l'état haut (niveau logique 1), tandis que les autres sorties sont maintenues à l'état bas (niveau logique 0). Ainsi, une seule sortie peut être active (à l'état haut) à la fois. Par conséquent, la ligne de sortie à l'état haut identifie le code binaire présent en entrée ; autrement dit, elle décode l'entrée binaire. Certains décodeurs binaires possèdent une broche d'entrée supplémentaire, nommée « Activation », qui contrôle les sorties du dispositif. Cette entrée supplémentaire permet d'activer ou de désactiver les sorties des décodeurs selon les besoins. Ce type de décodeur binaire est couramment utilisé comme décodeur d'adresse mémoire dans les applications de mémoire des microprocesseurs. |

This simple example above of a 2-to-4 line binary decoder consists of an

array of four AND gates. The 2 binary inputs labelled A and B are decoded into one of 4 outputs, hence the description of 2-to-4 binary decoder. Each output represents one of the miniterms of the 2 input variables, (each output = a miniterm). The binary inputs A and B determine which output line from Q0 to Q3 is “HIGH” at logic level “1” while the remaining outputs are held “LOW” at logic “0”. So only one output can be active (HIGH) at any one time. Therefore, whichever output line is “HIGH” identifies the binary code present at the input, in other words it “de-codes” the binary input. Some binary decoders have an additional input pin labelled “Enable” that controls the outputs from the device. This extra input allows the decoders outputs to be turned “ON” or “OFF” as required. These types of binary decoders are commonly used as “memory address decoders” in microprocessor memory applications. |

|

|

|

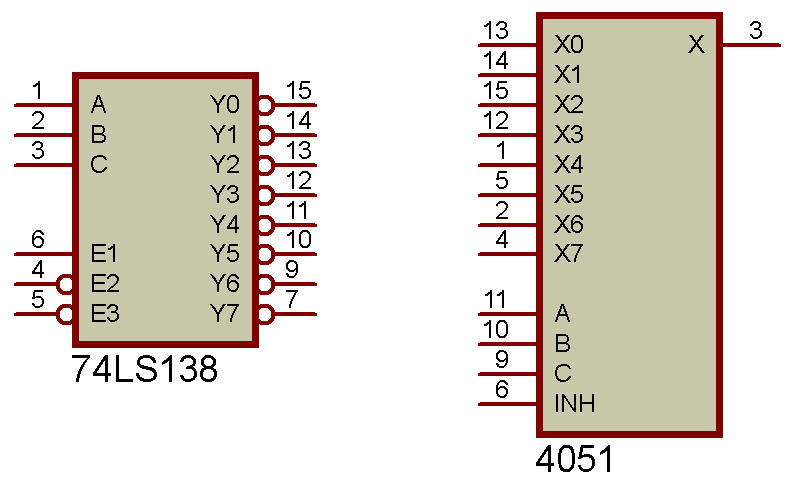

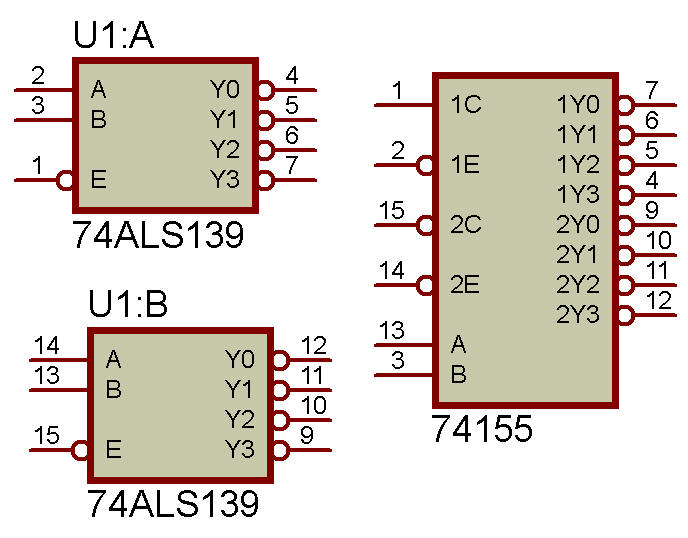

On peut dire qu'un décodeur binaire est un démultiplexeur doté d'une

ligne de données supplémentaire permettant son fonctionnement. Une autre façon d'appréhender le circuit du décodeur consiste à considérer les entrées A, B et C comme des signaux d'adresse. Chaque combinaison de A, B ou C définit une adresse mémoire unique. Nous avons vu qu'un décodeur binaire 2 vers 4 lignes (TTL 74155 ou 74ALS139) peut décoder n'importe quel code binaire 2 bits et fournir quatre sorties, une pour chaque combinaison d'entrées possible. |

We can say that a binary decoder is a demultiplexer with an additional

data line that is used to enable the decoder. An alternative way of looking at the decoder circuit is to regard inputs A, B and C as address signals. Each combination of A, B or C defines a unique memory address. We have seen that a 2-to-4 line binary decoder (TTL 74155 or 74ALS139) can be used for decoding any 2-bit binary code to provide four outputs, one for each possible input combination. |

|

|

|

Cependant, il arrive qu'un décodeur binaire ait besoin d'un nombre de

sorties supérieur à celui disponible. En ajoutant des entrées, le décodeur peut potentiellement fournir 2n sorties supplémentaires. |

However, sometimes it is required to have a Binary Decoder with a number

of outputs greater than is available. So by adding more inputs, the decoder can potentially provide 2n more outputs. |

|

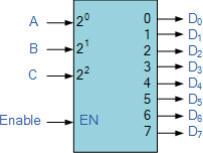

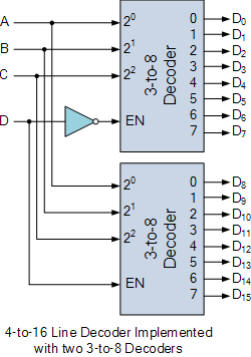

Par exemple, un décodeur à 3 entrées binaires (n = 3) produirait un

décodeur 3 vers 8 lignes (TTL 74138), et un décodeur à 4 entrées (n = 4)

produirait un décodeur 4 vers 16 lignes (TTL 74154), et ainsi de suite. Cependant, un décodeur peut également avoir moins de 2n sorties, comme le décodeur BCD vers sept segments (TTL 7447, Décodeurs BCD vers 7 segments), qui possède 4 entrées et seulement 7 sorties actives pour piloter un afficheur, au lieu des 16 (24) sorties attendues. Ici, un décodeur binaire 4 (3 entrées de données et 1 entrée d'activation) vers 16 lignes, beaucoup plus grand, a été implémenté à l'aide de deux décodeurs 3 vers 8 plus petits. |

So for example, a decoder with 3 binary inputs ( n = 3 ), would produce

a 3-to-8 line decoder (TTL 74138) and 4 inputs ( n = 4 ) would produce a

4-to-16 line decoder (TTL 74154) and so on. But a decoder can also have less than 2n outputs such as the BCD to seven-segment decoder (TTL 7447, BCD-to-7-segment decoders) which has 4 inputs and only 7 active outputs to drive a display rather than the full 16 (24) outputs as you would expect. Here a much larger 4 (3 data plus 1 enable) to 16 line binary decoder has been implemented using two smaller 3-to-8 decoders. |

|

|

|

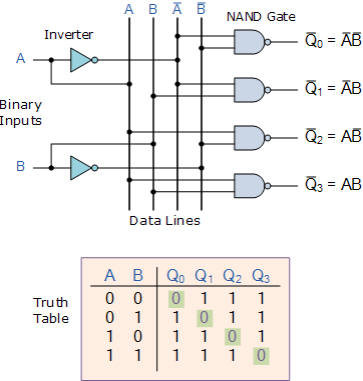

Les entrées A, B et C servent à sélectionner la sortie du décodeur qui

sera à l'état logique « 1 » (HAUT). L'entrée D, combinée à l'entrée d'activation, permet de sélectionner le décodeur (premier ou second) qui produira la sortie « 1 ». Cependant, le nombre d'entrées utilisables pour un décodeur donné est limité. En effet, lorsque n augmente, le nombre de portes ET nécessaires pour produire une sortie augmente également, ce qui accroît la charge des portes utilisées pour les piloter. Ce type de décodeur actif à l'état haut peut être implémenté uniquement à l'aide d'inverseurs (portes NON) et de portes ET. Il est pratique d'utiliser une porte ET comme élément de décodage de base pour la sortie, car elle ne produit une sortie à l'état haut (ou « 1 » logique) que lorsque toutes ses entrées sont à l'état logique haut. Cependant, certains décodeurs binaires utilisent des portes NAND plutôt que des portes AND pour leur sortie décodée, car les portes NAND sont moins coûteuses à produire, nécessitant moins de transistors. L'utilisation de portes NAND comme élément de décodage produit une sortie active à l'état bas (LOW), tandis que les autres sorties sont à l'état haut (HIGH). Comme une porte NAND effectue l'opération AND avec une sortie inversée, le décodeur NAND se présente ainsi avec sa table de vérité inversée. |

Inputs A, B, C are used to select which output on either decoder will be

at logic “1” (HIGH). And input D is used with the enable input to select which encoder either the first or second will output the “1”. However, there is a limit to the number of inputs that can be used for one particular decoder. Because as n increases, the number of AND gates required to produce an output also becomes larger resulting in the fan-out of the gates used to drive them becoming large. This type of active-“HIGH” decoder can be implemented using just Inverters, ( NOT Gates ) and AND gates. It is convenient to use an AND gate as the basic decoding element for the output because it produces a “HIGH” or logic “1” output only when all of its inputs are logic “1”. But some binary decoders are constructed using NAND gates instead of AND gates for their decoded output, since NAND gates are cheaper to produce than AND’s as they require fewer transistors to implement within their design. The use of NAND gates as the decoding element, results in an active-“LOW” output while the rest will be “HIGH”. As a NAND gate produces the AND operation with an inverted output, the NAND decoder looks like this with its inverted truth table. |

|

|

|

Dans un décodeur NAND, une seule sortie peut être à l'état bas (niveau

logique « 0 ») à un instant donné, toutes les autres sorties étant à

l'état haut (niveau logique « 1 »). Certains décodeurs sont également disponibles avec une entrée d'activation supplémentaire (EN) permettant d'activer ou de désactiver la sortie décodée en lui appliquant respectivement un niveau logique « 1 » ou « 0 ». Ainsi, par exemple, lorsque l'entrée d'activation est à l'état logique « 0 » (EN = 0), toutes les sorties sont à l'état bas (niveau logique « 0 ») pour les portes ET, quel que soit l'état des entrées A et B. Généralement, pour implémenter cette fonction d'activation, les portes ET ou NAND à 2 entrées sont remplacées par des portes ET ou NAND à 3 entrées. La broche d'entrée supplémentaire représente la fonction d'activation. |

Then for the NAND decoder, only one output can be LOW and equal to logic

“0” at any given time, with all the other outputs being HIGH at logic “1”. Decoders are also available with an additional “Enable” input pin which allows the decoded output to be turned “ON” or “OFF” by applying a logic “1” or logic “0” respectively to it. So for example, when the enable input is at logic level “0”, (EN = 0) all outputs are “OFF” at logic “0” (for AND gates) regardless of the state of the inputs A and B. Generally to implement this enabling function the 2-input AND or NAND gates are replaced with 3-input AND or NAND gates. The additional input pin represents the enable function. |

|

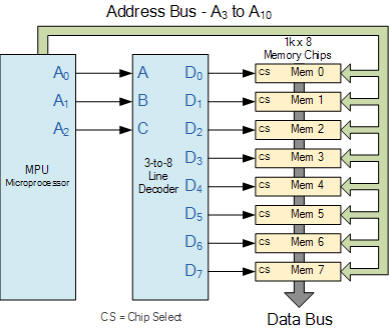

Décodeur d'adresse mémoire Les décodeurs binaires sont principalement utilisés dans les systèmes numériques complexes pour accéder à un emplacement mémoire spécifique à partir d'une « adresse » générée par un dispositif informatique. Dans les systèmes à microprocesseur modernes, la quantité de mémoire requise peut être très importante et dépasse généralement le volume d'une seule puce mémoire. Une solution à ce problème consiste à connecter plusieurs puces mémoire individuelles et à lire les données sur un bus de données commun. Afin d'éviter la lecture simultanée des données de chaque puce mémoire, chaque puce est sélectionnée individuellement, l'une après l'autre. Ce processus est appelé décodage d'adresse. Dans ce type d'application, l'adresse représente les données d'entrée codées, et les sorties sont les signaux de sélection de l'élément mémoire. Chaque puce mémoire possède une entrée appelée sélection de puce (CS), utilisée par le microprocesseur (MPU) pour sélectionner la puce mémoire appropriée en cas de besoin. En général, un niveau logique « 1 » sur l'entrée de sélection de puce (CS) sélectionne le périphérique mémoire, tandis qu'un niveau logique « 0 » le désélectionne. Ainsi, la sélection ou la désélection de chaque puce individuellement permet de choisir le périphérique mémoire correspondant à une adresse donnée. L'avantage du décodage d'adresse est que, lorsqu'une adresse mémoire est spécifiée, l'emplacement mémoire correspondant se trouve UNIQUEMENT sur l'une des puces. Par exemple, supposons un système à microprocesseur très simple doté de 1 Ko (mille octets) de mémoire RAM et de 10 lignes d'adresse disponibles. La mémoire est composée de dispositifs de 128 × 8 bits (128 × 8 = 1 024 bits). Pour 1 Ko, il faudrait 8 puces mémoire individuelles. Cependant, pour sélectionner la puce mémoire appropriée, un décodeur binaire 3 vers 8 lignes est également nécessaire, comme illustré ci-dessous. |

Memory Address Decoder Binary Decoders are most often used in more complex digital systems to access a particular memory location based on an “address” produced by a computing device. In modern microprocessor systems the amount of memory required can be quite high and is generally more than one single memory chip alone. One method of overcoming this problem is to connect lots of individual memory chips together and to read the data on a common “Data Bus”. In order to prevent the data being “read” from each memory chip at the same time, each memory chip is selected individually one at time and this process is known as Address Decoding. In this type of application, the address represents the coded data input, and the outputs are the particular memory element select signals. Each memory chip has an input called Chip Select or CS which is used by the MPU (micro-processor unit) to select the appropriate memory chip when required. Generally a logic “1” on the chip select (CS) input selects the memory device while a logic “0” on the input de-selects it. So by selecting or de-selecting each chip one at a time, allows us to select the correct memory address device for a particular address location. The advantage of address decoding is that when we specify a particular memory address, the corresponding memory location exists ONLY in one of the chips. For example, Lets assume we have a very simple microprocessor system with only 1Kb (one thousand bytes) of RAM memory and 10 memory address lines available. The memory consists of 128×8-bit (128×8 = 1024 bits) devices and for 1Kb we would need 8 individual memory chips. But in order to select the correct memory chip we would also require a 3-to-8 line binary decoder as shown below. |

|

|

|

Le décodeur binaire n'a besoin que de trois lignes d'adresse (A0 à A2)

pour sélectionner chacune des huit puces (la partie inférieure de

l'adresse), tandis que les huit lignes restantes (A3 à A10)

sélectionnent l'emplacement mémoire correspondant sur cette puce (la

partie supérieure de l'adresse). Une fois l'emplacement mémoire sélectionné via le bus d'adresses, les informations qu'il contient sont envoyées à un bus de données commun pour être utilisées par le microprocesseur. Il s'agit bien sûr d'un exemple simplifié, mais les principes restent les mêmes pour tous les types de puces ou de modules mémoire. |

The binary decoder requires only 3 address lines, (A0 to A2) to select

each one of the 8 chips (the lower part of the address), while the

remaining 8 address lines (A3 to A10) select the correct memory location

on that chip (the upper part of the address). Having selected a memory location using the address bus, the information at the particular internal memory location is sent to a common “Data Bus” for use by the microprocessor. This is of course a simple example but the principals remain the same for all types of memory chips or modules. |

|

Les décodeurs binaires sont des dispositifs très utiles pour convertir

un format numérique en un autre, comme des données de type binaire ou

BCD en décimal ou octal, etc. Les circuits intégrés de décodeurs couramment disponibles sont le décodeur binaire TTL 74LS138 de 3 à 8 lignes ou le décodeur 74ALS154 de 4 à 16 lignes. |

Binary Decoders are very useful devices for converting one digital

format to another, such as binary or BCD type data into decimal or octal

etc. And commonly available decoder IC’s are the TTL 74LS138 3-to-8 line binary decoder or the 74ALS154 4-to-16 line decoder. |

| Voir / See Sélecteur TTL (Porte ET, NON-OU, NON-ET) | |

|

|

|

|