Il existe deux types d'additionneurs binaires :

Les

demi-additionneurs et les additionneurs complets.

Un

demi-additionneur additionne des nombres binaires de 2 bits, mais ne

peut pas inclure la retenue.

À l'inverse, un additionneur complet

additionne la retenue avec les deux nombres binaires, ce qui permet

d'additionner des nombres binaires multibits en cascadant plusieurs

additionneurs complets.

|

Binary adders come in two types:

Half Adders and Full Adders.

A half adder adds 2-bit binary numbers but cannot include a

carry bit.

In contrast, a Full Adder adds the carry bit along

with the two binary numbers, enabling the addition of multi-bit binary

numbers by cascading multiple Full Adder circuits.

|

Demi-additionneur

Un circuit numérique utilisé pour

effectuer l'addition de nombres est appelé un additionneur dans le

domaine électrique et électronique.

En électronique et en

informatique, les nombres sont généralement exprimés en binaire, où 0

représente un niveau logique bas et 1 un niveau logique haut.

Pour réaliser des tâches complexes, ces 0 et 1 sont souvent traités par

des opérations arithmétiques :

addition, soustraction,

multiplication et division.

|

Half Adder

A digital circuit used to carry out the

addition of numbers is called an adder in the electrical/electronic

field.

In the electronics/digital field usually, numbers are

expressed in a binary format where 0 represents a logic low and 1

represents a logic high.

To carry out complex tasks in the

digital world often these simple 0s and 1s are processed using

arithmetic operations i.e. addition, subtraction, multiplication, and

division.

|

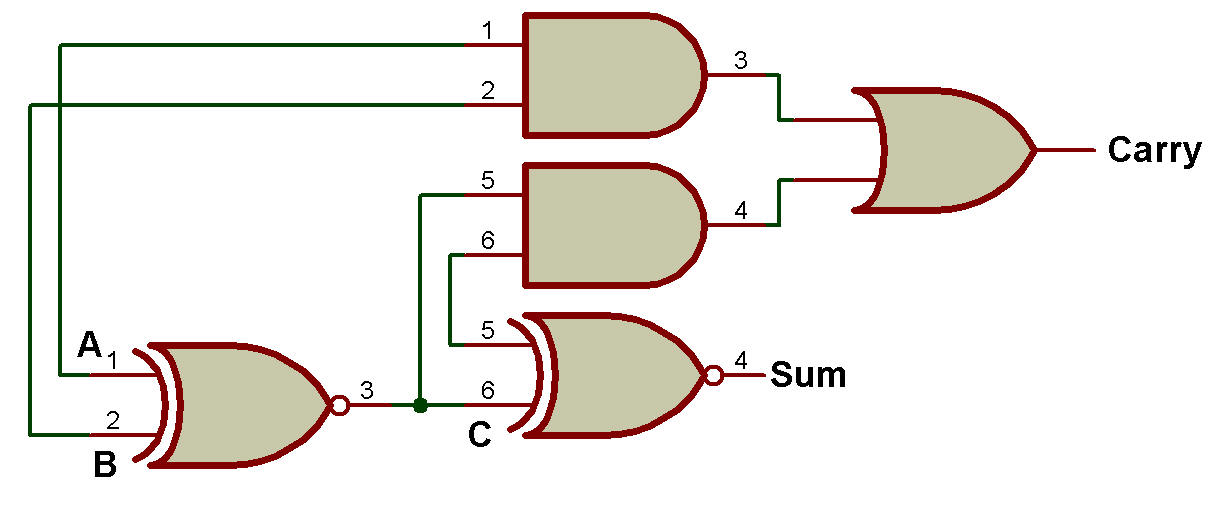

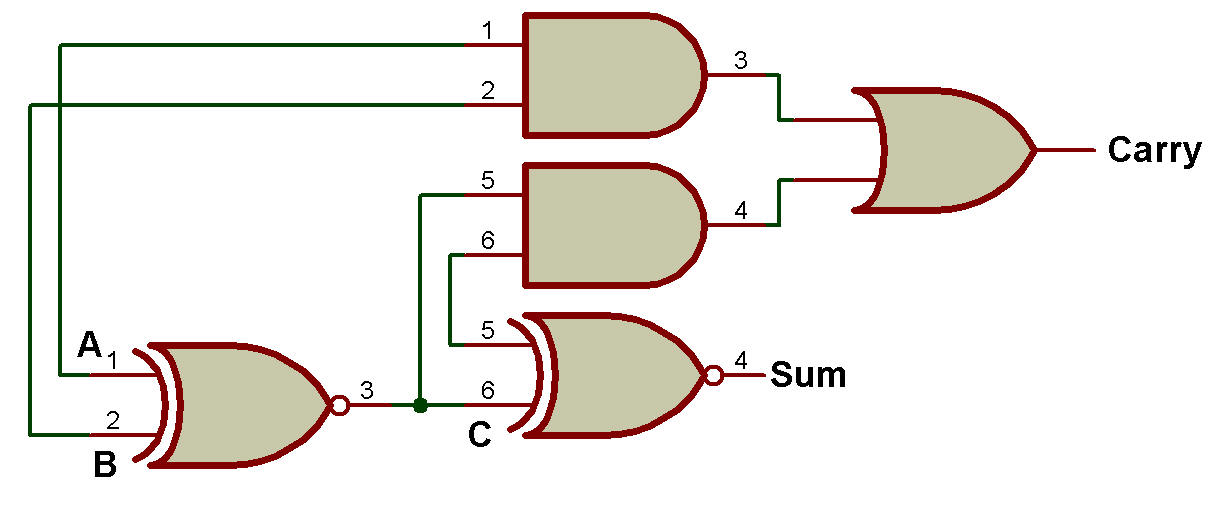

Un circuit capable d'effectuer cette tâche simple, à savoir fournir la

somme résultante et la retenue en sortie, peut être construit à l'aide

de portes logiques simples, comme illustré ci-dessous :

|

A circuit that can carry out this simple task to give resultant sum and

carry as output can be built using simple gates as shown below:

|

|

|

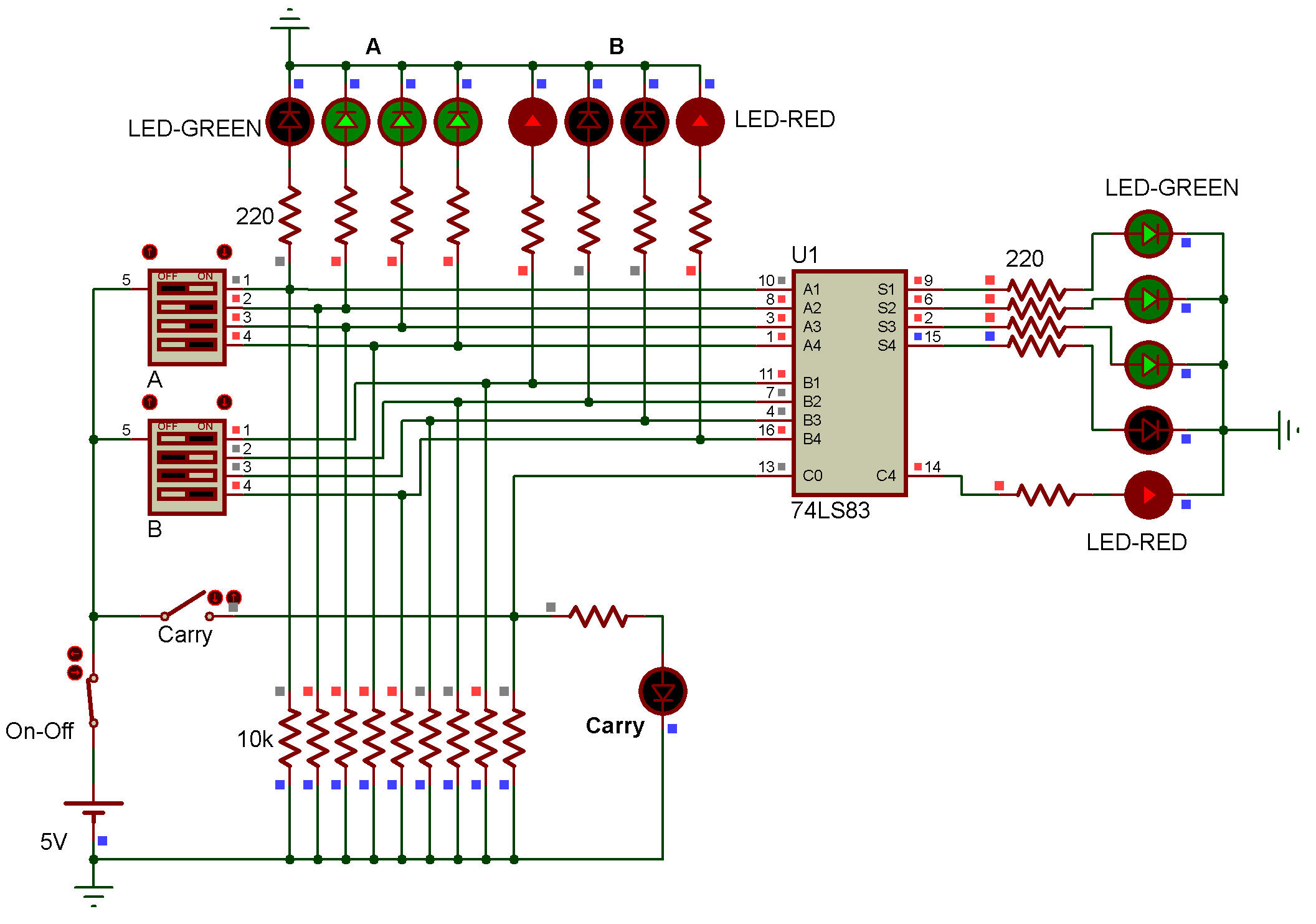

Un circuit capable d'effectuer cette tâche peut être construit à

l'aide de portes logiques comme suit.

L'avantage d'un

additionneur complet est qu'en cascadant deux additionneurs complets ou

plus, on peut effectuer l'addition de nombres composés de plusieurs

bits. |

A circuit that can perform this task can be built using gates as

follows.

The advantage of a full adder is that by cascading two

or more full adders we can perform the addition of numbers consisting of

multiple bits.

|

|

|

|

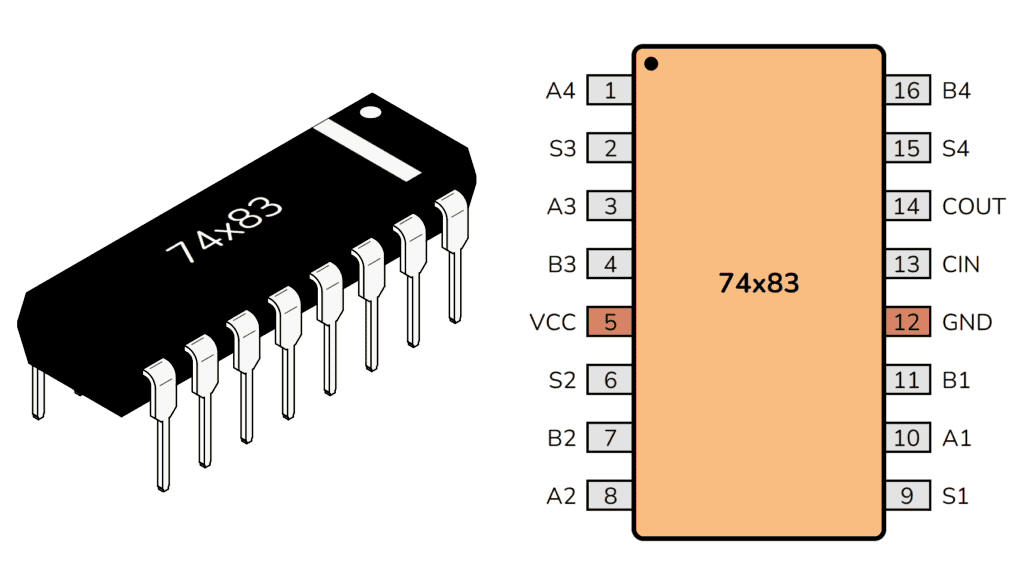

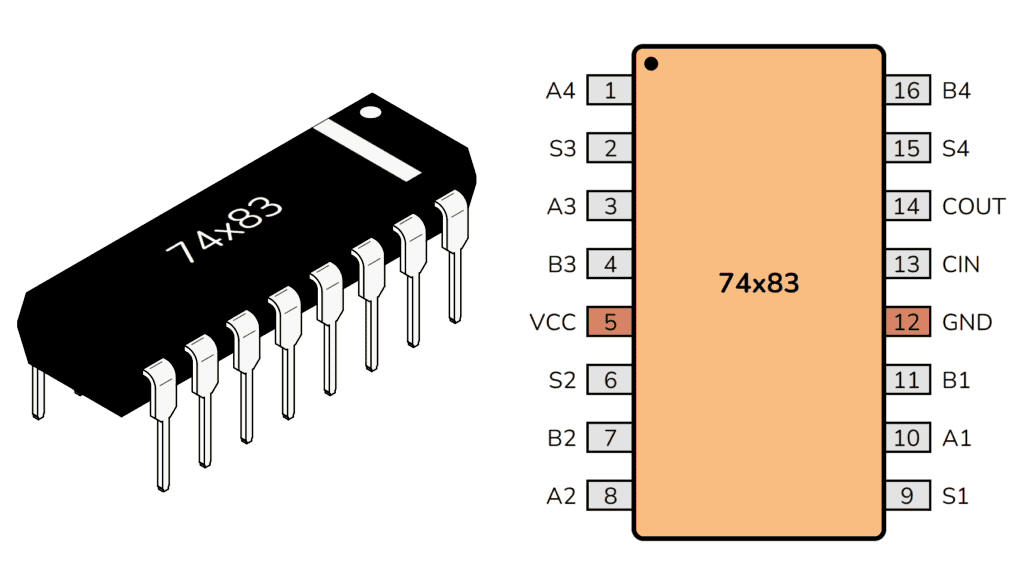

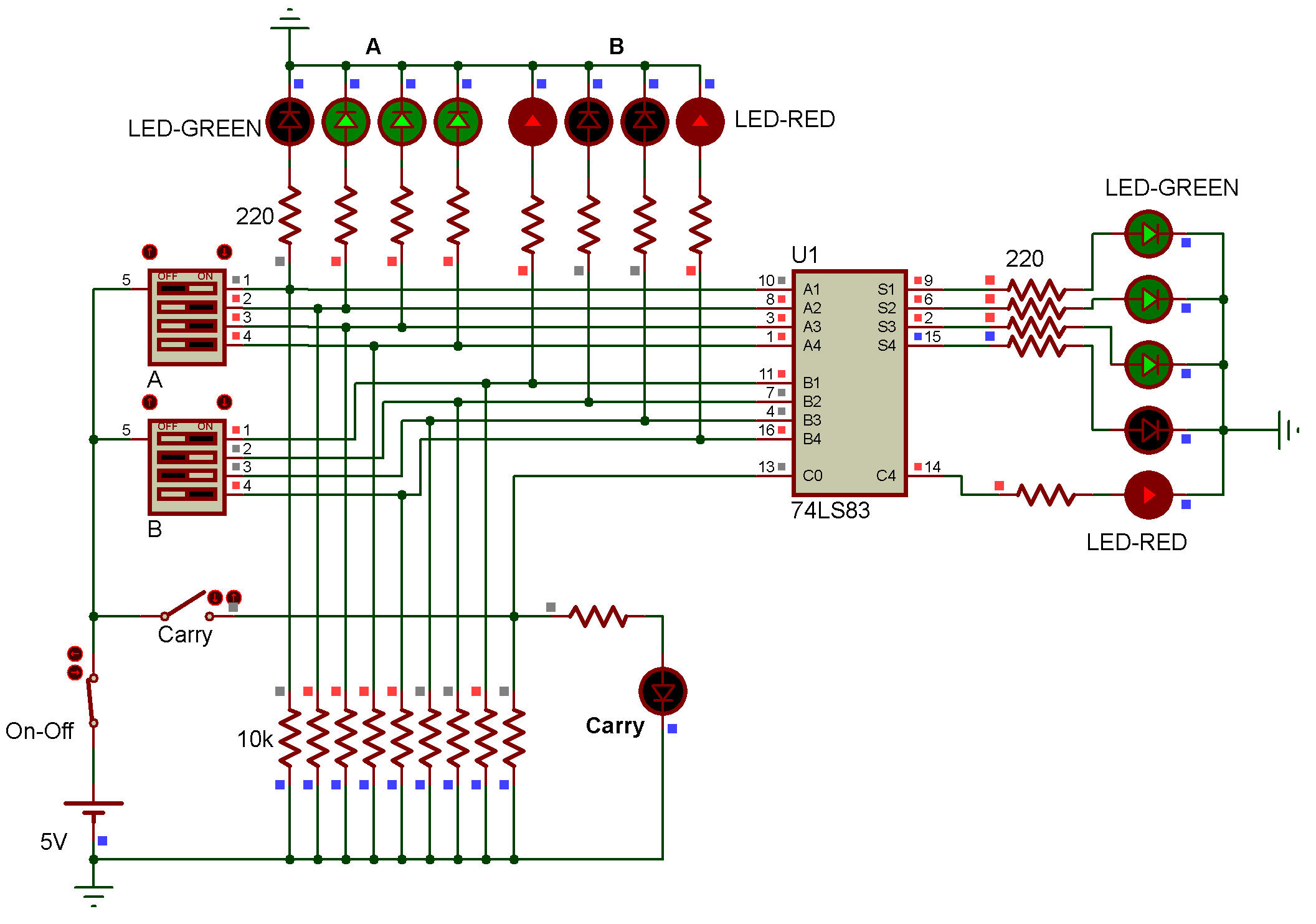

74LS83 4-Bit Full Adder Pin Out

|

Ce circuit intégré possède 16 broches.

Les broches 5 et 12

servent respectivement à alimenter le circuit intégré avec +5 V et la

masse (GND).

Considérons deux nombres de 4 bits :

A4 A3

A2 A1 et B4 B3 B2 B1

où A1 et B1 représentent les bits de poids

faible (LSB) de ces nombres.

A4 et B4 représentent les bits de

poids fort (MSB) de ces mêmes nombres.

Les broches 1, 3, 8 et 10

sont des entrées et servent à fournir les bits du premier nombre (A4 A3

A2 A1).

Les broches 16, 4, 7 et 11 sont des entrées et servent à

fournir les bits du second nombre (B4 B3 B2 B1).

La broche 13 est

une entrée et sert à fournir la retenue.

Les broches 15, 2, 6 et

9 sont des sorties et servent à observer l'addition des deux nombres :

S4 S3 S2 S1.

La broche n° 14 est une broche de sortie et affiche

la retenue résultante de l'addition. |

This IC has a total of 16 pins.

Pin# 5 and 12 are used to power

up IC with +5V and GND terminal of power supply respectively.

Let

say we have two 4 bit numbers as

A4 A3 A2 A1 and B4 B3 B2 B1

with A1 and B1 as Least Significant Bit (LSB) of respective numbers.

A4 and B4 as Most Significant Bit (MSB) of the same numbers.

Pin#1,3,8,10 are input pins and will be used to feed A4 A3 A2 A1 bit

of 1 number

Pin#16,4,7,11 are input pins and will be used to B4

B3 B2 B1 bit of 2 number.

Pin#13 is an input pin and used to

feed carry in.

Pin#15,2,6,9 are output pins and will be used to

observe the addition of two above numbers as S4 S3 S2 S1.

Pin# 14

is an output pin and displays the resultant carry of addition.

|

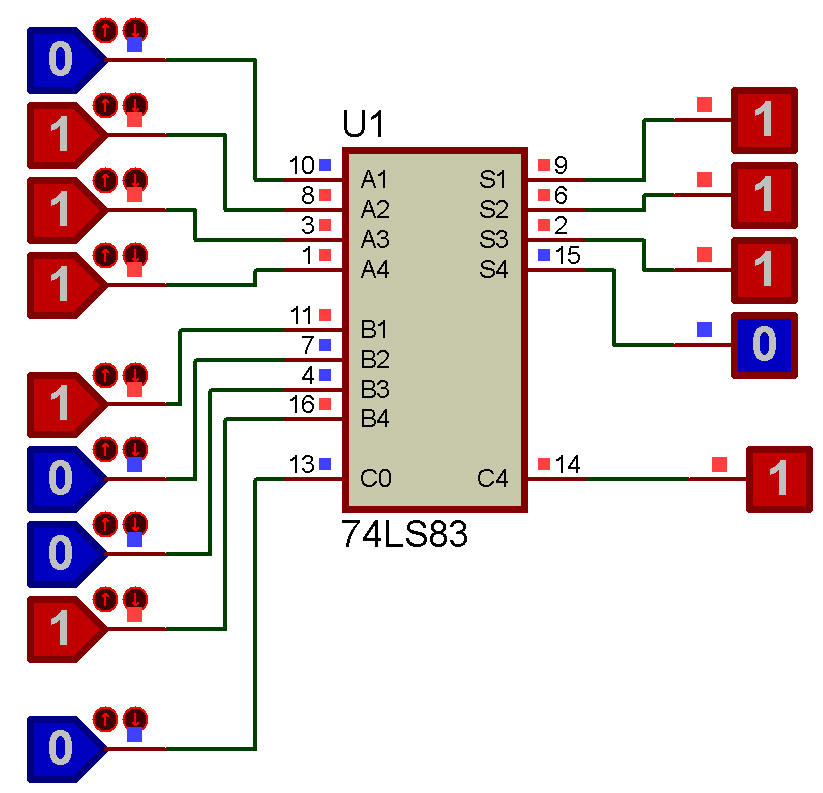

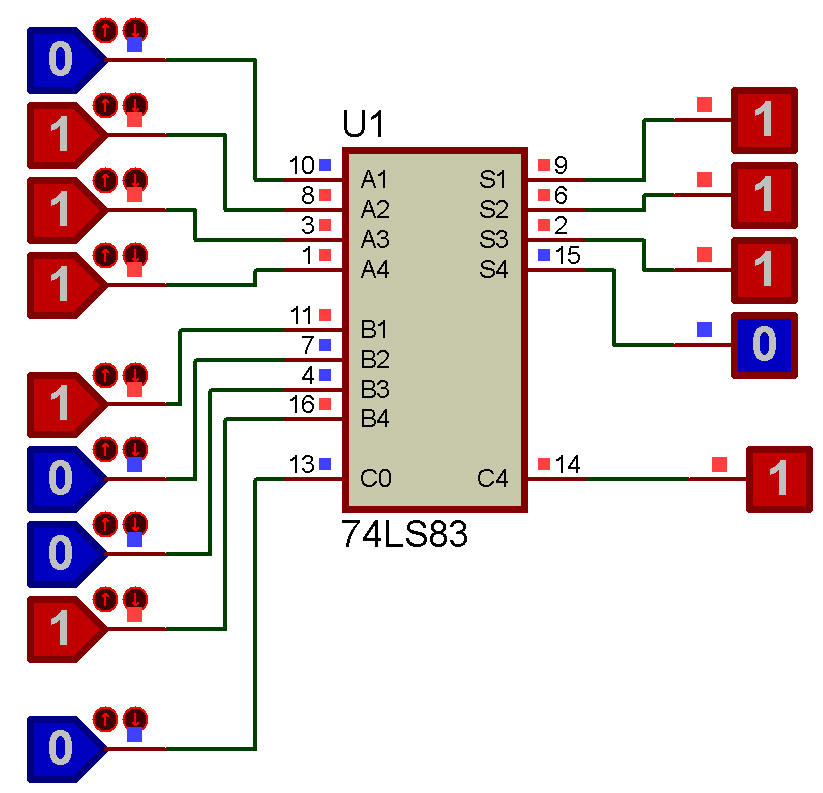

Supposons que nous ayons deux nombres :

1110 (14) sous la forme

A4 A3 A2 A1

et 1001 (9) sous la forme B4 B3 B2 B1

avec une

retenue C0 égale à 0.

Le résultat devrait être 10111 (23) sous la

forme C4 S4 S3 S2 S1, comme illustré dans l'image ci-dessous.

|

Suppose we have two numbers

1110 (14) as A4 A3 A2 A1

and

1001 (9) as B4 B3 B2 B1

with carry C0 as 0.

The

resultant should be 10111 (23) as C4 S4 S3 S2 S1 and it can be observed

in the pic below.

|

|

|

Multiplicateur

|

Multiplier

|

Un multiplicateur binaire est un circuit logique combinatoire utilisé

dans les systèmes numériques pour effectuer la multiplication de deux

nombres binaires.

On les retrouve fréquemment dans diverses

applications, notamment dans le domaine du traitement numérique du

signal, pour exécuter différents algorithmes.

Des applications

commerciales telles que les ordinateurs, les téléphones portables, les

calculatrices rapides et certains processeurs à usage général

nécessitent des multiplicateurs binaires.

Comparée à l'addition

et à la soustraction, la multiplication est une opération plus complexe.

Lors d'une multiplication, le nombre par lequel on multiplie l'autre

est appelé multiplicande, et le nombre résultant est appelé

multiplicateur.

|

A binary multiplier is a combinational logic circuit used in digital

systems to perform the multiplication of two binary numbers.

These are most commonly used in various applications especially in the

field of digital signal processing to perform the various algorithms.

Commercial applications like computers, mobiles, high speed

calculators and some general purpose processors require binary

multipliers.

Compared with addition and subtraction, multiplication is a complex

process.

In multiplication process, the number which is to be

multiplied by the other number is called as multiplicand and the number

multiplied is called as multiplier.

|

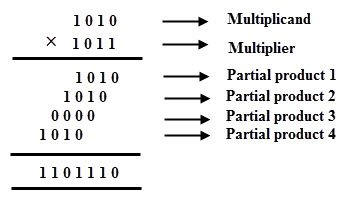

Multiplication binaire

Comme pour la multiplication des

nombres décimaux, la multiplication binaire suit le même processus pour

obtenir le produit de deux nombres binaires.

La multiplication

binaire est beaucoup plus simple car elle ne contient que des 0 et des

1.

Les quatre règles fondamentales de la multiplication binaire

sont :

0 × 0 = 0

0 × 1 = 0

1 × 0 = 0

1 × 1 =

1

La multiplication de deux nombres binaires peut être effectuée

à l’aide de deux méthodes courantes :

l’addition partielle et le

décalage, ou encore à l’aide de multiplicateurs parallèles.

Avant

d’aborder les différents types de multiplication, examinons le processus

de multiplication des nombres binaires non signés.

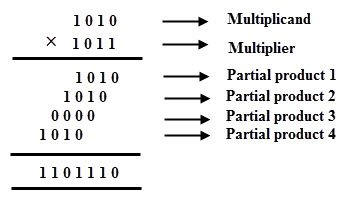

Prenons deux

nombres binaires de 4 bits, 1010 et 1011. Leur produit est donné par :

|

Binary Multiplication

Similar to the multiplication of

decimal numbers, binary multiplication follows the same process for

producing a product result of the two binary numbers.

The binary

multiplication is much easier as it contains only 0s and 1s.

The

four fundamental rules for binary multiplication are

0 × 0 = 0

0 × 1 = 0

1 × 0 = 0

1 × 1 = 1

The multiplication of

two binary numbers can be performed by using two common methods, namely

partial product addition and shifting, and using parallel multipliers.

Before discussing about the types, let us look at the unsigned

binary numbers multiplication process.

Consider a two 4 bit

binary numbers as 1010 and 1011, and its multiplication of these two is

given as

|

|

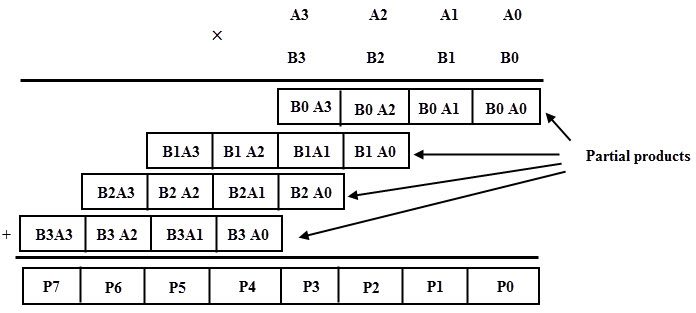

À partir de la multiplication ci-dessus, des produits partiels sont

générés pour chaque bit du multiplicateur.

Ces produits partiels

sont ensuite additionnés pour obtenir la valeur finale du produit.

Dans la multiplication par produits partiels, lorsque le bit du

multiplicateur est à zéro, le produit partiel est nul ; lorsqu'il est à

1, le produit partiel résultant est le multiplicande.

Comme pour

les nombres décimaux, chaque produit partiel successif est décalé d'une

position vers la gauche par rapport au produit partiel précédent avant

d'être additionné.

Ainsi, cette multiplication utilise n

décalages et n additions pour multiplier un nombre binaire de n bits.

Le circuit combinatoire implémenté pour effectuer une telle

multiplication est appelé multiplicateur matriciel ou multiplicateur

combinatoire. |

From the above multiplication, partial products are generated for each

digit in the multiplier.

Then all these partial products are

added to produce the final product value.

In the partial product

multiplication, when the multiplier bit zero, the partial product is

zero, and when the multiplier bit is 1, the resulted partial product is

the multiplicand.

As similar to the decimal numbers, each

successive partial product is shifted one position left relative to the

preceding partial product before summing all partial products.

Therefore, this multiplication uses n-shifts and adds to multiply n-bit

binary number.

The combinational circuit implemented to perform

such multiplication is called as an array multiplier or combinational

multiplier.

|

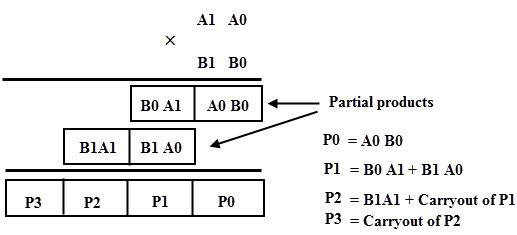

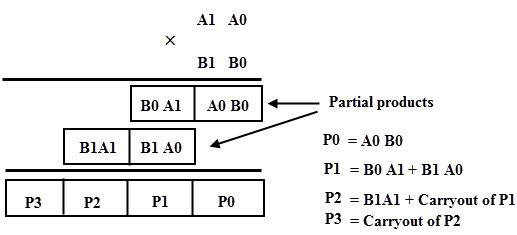

Multiplicateur binaire parallèle

Considérons deux nombres

binaires non signés de 2 bits, A et B, afin de généraliser le processus

de multiplication.

Le multiplicande A est égal à A₁A₀ et le

multiplicateur B est égal à B₁B₀.

La figure ci-dessous illustre

le processus de multiplication de deux nombres binaires de 2 bits. |

Parallel Binary Multiplier

Let us consider two unsigned 2

bit binary numbers A and B to generalize the multiplication process.

The multiplicand A is equal to

A₁A₀ and the multiplier B is equal to

B₁B₀.

The figure below shows the multiplication process

of two 2 bit binary numbers.

|

|

Ce processus implique la multiplication de deux chiffres et l'addition

de chiffres avec ou sans retenue.

Après la multiplication de

chaque bit par le multiplicande, les produits partiels sont générés,

puis additionnés pour obtenir la somme totale, qui représente le

résultat binaire de la multiplication.

Cette multiplication est

implémentée par un circuit combinatoire : la multiplication est réalisée

à l'aide de portes ET, tandis que l'addition est effectuée à l'aide de

demi-additionneurs, comme illustré sur la figure. |

This process involves the multiplication of two digits and the addition

of digits with or without carry.

After the multiplication of the

each bit to the multiplicand, partial products are generated, and then

these products are added to produce the total sum which represents the

binary multiplication value.

This multiplication is implemented

by combinational circuit such that the multiplication is performed with

AND gates whereas the addition is carried out by using half adders as

shown in figure.

|

|

Le premier produit partiel est obtenu par la porte ET et correspond au

bit de poids faible du résultat de la multiplication.

Comme le

second produit partiel est décalé vers la gauche, le second terme du

premier produit partiel et le premier terme du second sont additionnés

par un demi-additionneur, produisant ainsi la somme et la retenue.

Cette retenue est ensuite ajoutée à l'entrée du demi-additionneur

suivant, comme illustré sur la figure.

De même, ce circuit simple

permet de calculer le résultat de la multiplication de deux nombres

binaires.

La multiplication de deux nombres de 2 bits donne un

nombre binaire de 4 bits.

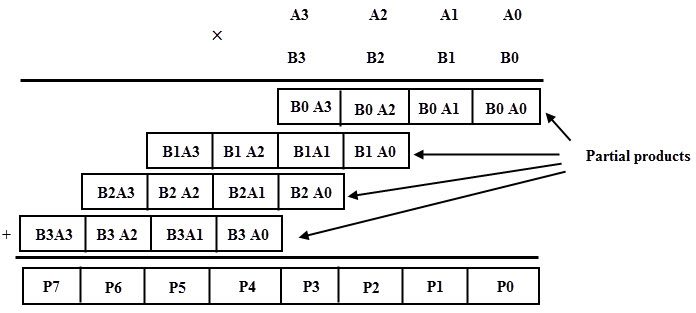

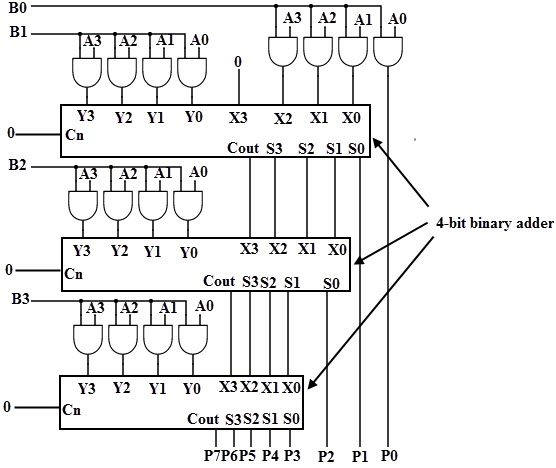

Considérons la multiplication de deux

nombres non signés de 4 bits, où le multiplicande A est égal à A3A2A1A0

et le multiplicateur B est égal à B3B2B1B0.

Les produits partiels

sont calculés en fonction de chaque bit du multiplicateur multiplié par

le multiplicande.

Chaque produit partiel est composé de quatre

termes, décalés vers la gauche par rapport au produit partiel précédent,

comme illustré sur la figure.

Tous ces produits partiels sont

additionnés pour produire le produit 8 bits.

|

The first partial product is obtained by the AND gate which is nothing

but a least significant bit of the multiplication result.

Since

the second partial product is shifted to the left position, the first

partial second term and second partial product first term is added by

half adder and produce the sum output along with the carry out.

This carry out is added at the next half adder as an input as shown in

figure.

Likewise, it produces the multiplication result of two

binary numbers by using the simple circuit configuration.

The

multiplication of the two 2 bit number results a 4-bit binary number.

Let us consider two unsigned 4 bit numbers multiplication in

which the multiplicand, A is equal to A3A2 A1A0 and the multiplier B is

equal to B3B2B1B0.

The partial products are produced depending

on each multiplier bit multiplied by the multiplicand.

Each

partial product consists of four product terms and these are shifted to

the left relative to the previous partial product as shown in figure.

All these partial products are added to produce the 8 bit

product.

|

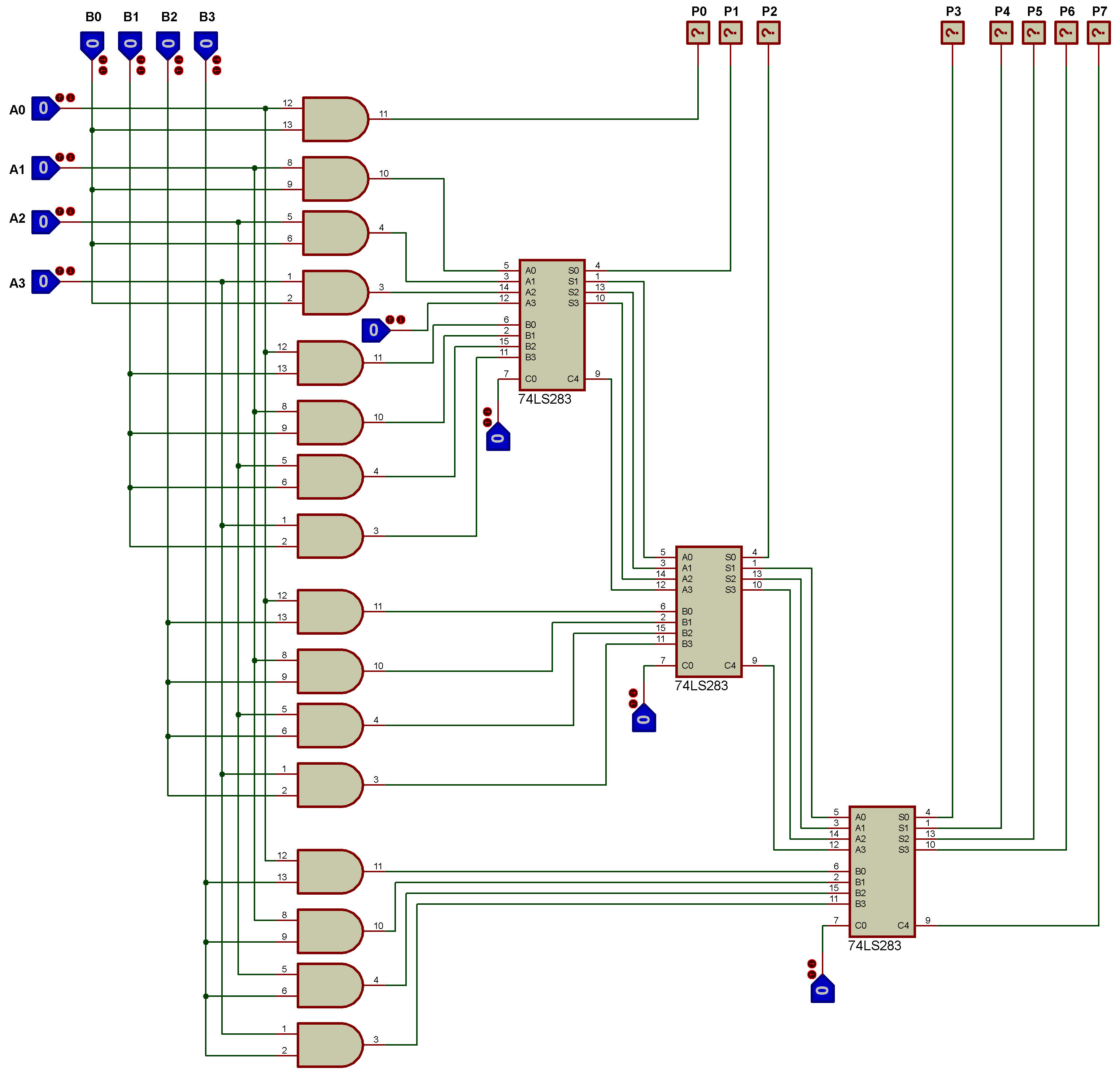

|

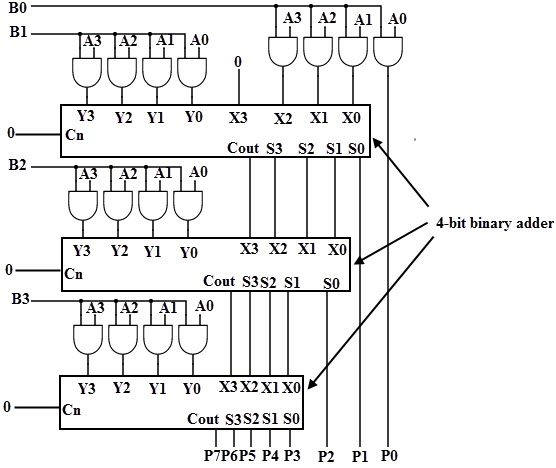

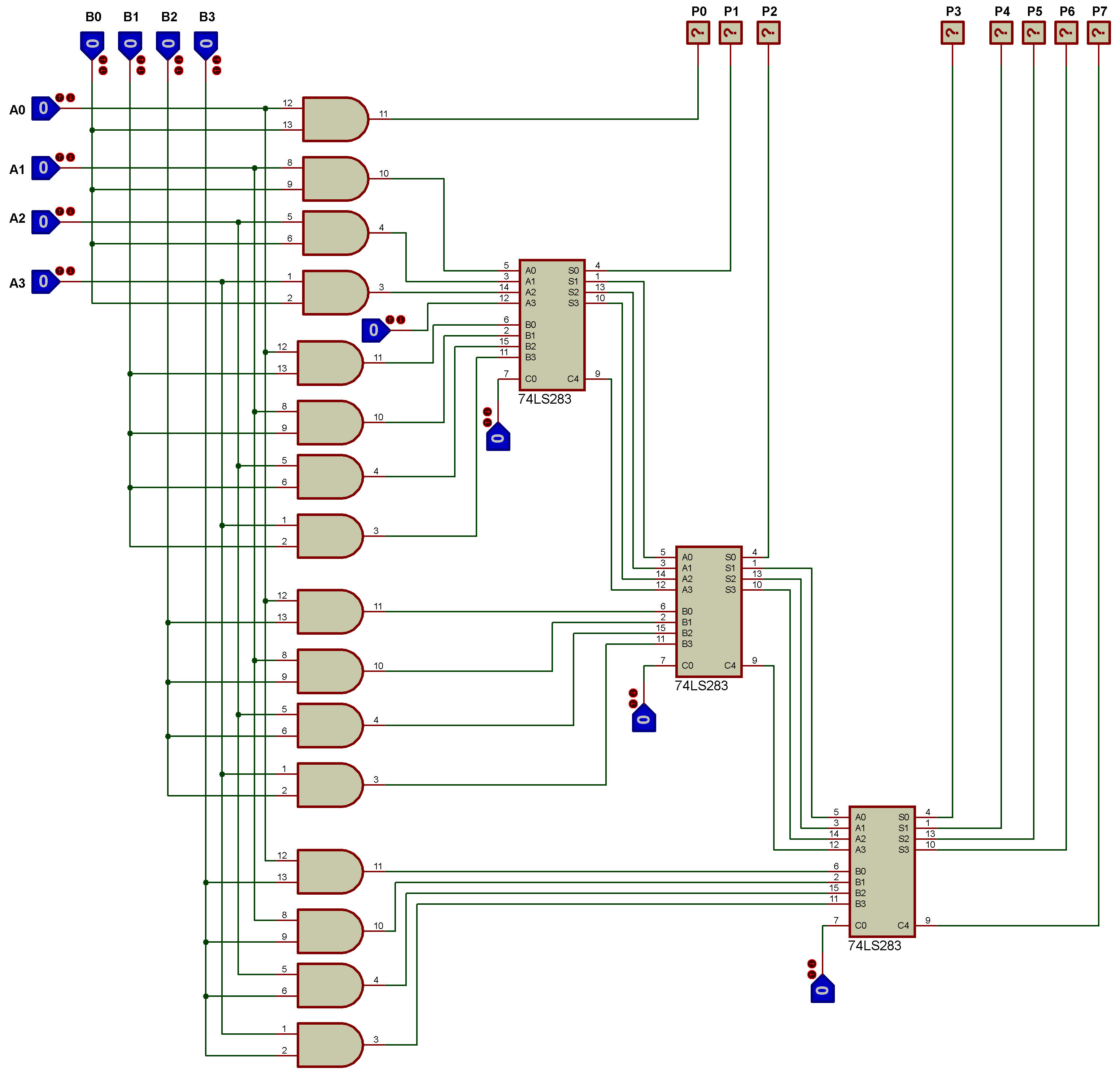

Le circuit logique de la multiplication binaire 4 × 4 peut être

implémenté à l'aide de trois additionneurs complets binaires et de

portes ET.

Dans l'opération décrite ci-dessus, le premier produit

partiel est obtenu en multipliant B0 par A3A2 A1A0, le deuxième par B1,

et ainsi de suite pour les troisième et quatrième produits partiels.

Ces produits partiels peuvent être implémentés à l'aide de portes

ET, comme illustré sur la figure.

Ces produits partiels sont

ensuite additionnés à l'aide d'un additionneur parallèle 4 bits.

Les trois bits de poids fort du premier produit partiel, avec la retenue

(considérée comme nulle), sont additionnés au deuxième produit partiel

dans le premier additionneur complet.

Le résultat est ensuite

additionné au produit partiel suivant, avec la retenue restante, et

ainsi de suite jusqu'au dernier produit partiel. On obtient ainsi une

somme de 8 bits qui indique le résultat du produit des deux nombres

binaires.

|

The logic circuit for the 4× 4 binary multiplication can be implemented

by using three binary full adders along with AND gates.

In the

above operation the first partial product is obtained by multiplying B0

with A3A2 A1A0, the second partial product is formed by multiplying B1

with A3A2 A1A0, likewise for 3rd and 4th partial products.

So

these partial products can be implemented with AND gates as shown in

figure.

These partial products are then added by using 4 bit

parallel adder.

The three most significant bits of first partial

product with carry (considered as zero) are added with second partial

term in the first full adder.

Then the result is added to the

next partial product with carry out and it goes on till the final

partial product, finally it produces 8 bit sum which indicates the

multiplication value of the two binary numbers.

|

|